# A 77-GHz Phased-Array Transceiver With On-Chip Antennas in Silicon: Receiver and Antennas

Aydin Babakhani, Student Member, IEEE, Xiang Guan, Member, IEEE, Abbas Komijani, Student Member, IEEE, Arun Natarajan, Student Member, IEEE, and Ali Hajimiri, Member, IEEE

Abstract—In this paper, we present the receiver and the on-chip antenna sections of a fully integrated 77-GHz four-element phased-array transceiver with on-chip antennas in silicon. The receiver section of the chip includes the complete down-conversion path comprising low-noise amplifier (LNA), frequency synthesizer, phase rotators, combining amplifiers, and on-chip dipole antennas. The signal combining is performed using a novel distributed active combining amplifier at an IF of 26 GHz. In the LO path, the output of the 52-GHz VCO is routed to different elements and can be phase shifted locally by the phase rotators. A silicon lens on the backside is used to reduce the loss due to the surface-wave power of the silicon substrate. Our measurements show a single-element LNA gain of 23 dB and a noise figure of 6.0 dB. Each of the four receive paths has a gain of 37 dB and a noise figure of 8.0 dB. Each on-chip antenna has a gain of +2 dBi.

*Index Terms*—BiCMOS, dielectric lens, integrated circuits, on-chip dipole antennas, phased-array, silicon germanium, surface wave.

## I. INTRODUCTION

CILICON technology has entered the realm of millimeter-wave frequencies by the sheer force of transistor scaling, unmatched levels of integration, low cost, and high yield. This has opened the door to a plethora of new applications, formerly accessible only to III-V semiconductors. There are several frequency bands in the millimeter-wave (mm-wave) range which have been approved by Federal Communications Commission (FCC) for wireless communications and automotive radar. These include the 24.05-24.25 GHz1 and 57–64 GHz bands for high speed wireless communications, and the 22-29 GHz and 76-77-GHz bands for automotive radar. Although the current industrial efforts at 77-GHz range are focused on automotive radar, a mm-wave wireless system can also be used for other applications, such as short-range surveillance, microwave imaging, and ultra-high-speed data transmission. Recently, several silicon-based systems have been reported that operate at these frequencies [2]–[5].

Manuscript received May 3, 2006; revised September 1, 2006. This work was supported in part by the National Science Foundation under Grant ECS-0239343.

A. Babakhani, A. Komijani, A. Natarajan, and A. Hajimiri are with the California Institute of Technology, Pasadena, CA 91125 USA (e-mail: aydin@caltech.edu).

X. Guan is with SiBEAM Inc., Sunnyvale, CA 94085 USA (e-mail: seanguan@gmail.com).

Digital Object Identifier 10.1109/JSSC.2006.884811

<sup>1</sup>Although technically speaking the millimeter frequency range starts at 30 GHz, the behavior and general considerations for 24-GHz systems are close enough to 30 GHz to be considered in that category for the purposes of our discussions.

Automobile radar operating in the 77-GHz frequency band is one such application as the 76–77-GHz band has been allocated for this purpose in many countries around the world [6]. Also, the Electronic Communications Committee (ECC) within the European Conference of Postal and Telecommunications Administrations has allocated the 77–81 GHz window for the automotive UWB short-range radar [7]. Compared to the radar bands at lower frequencies, such as the 22–29 GHz band, operating at 77-GHz band is more compatible with other applications in the nearby frequency spectrum. Meanwhile, the effective wavelength at 77 GHz on silicon is on the order of a millimeter which makes possible on-chip antennas that can significantly improve system reliability and repeatability, while lowering the cost by eliminating the last mm-wave electrical interfaces to the chip.

The objective of this work is to demonstrate a general purpose low-cost fully integrated phased-array receiver operating at 77 GHz using an on-chip antenna array. Besides implementing antennas on highly conductive silicon substrate, other design challenges of the system include a low-noise front-end, efficient and accurate phase shifting and signal combining, as well as high-speed frequency generation and distribution.

Historically, III-V compound semiconductors rather than silicon-based processes have been used to implement the mm-wave systems due to their high carrier mobility, high breakdown voltages, and lower passive loss. The low breakdown voltage of silicon transistors combined with poor metal conductivity make power generation at mm-wave frequencies challenging. In a standard silicon process the substrate is lossy due to its low substrate resistivity, which often is less than 10  $\Omega$  · cm. This is substantially smaller than that of GaAs substrates ( $10^7 - 10^9 \ \Omega \cdot \text{cm}$ ). Additionally, the high dielectric constant of silicon ( $\epsilon_{\rm r}\sim 11.7$ ) results in the silicon substrate absorbing most of the power in unshielded structures such as inductors, coplanar transmission lines and dipole antennas rather than allowing the energy to propagate in a desired manner or to radiate into free space. In the absence of appropriate preventive measures, the combination of high dielectric constant and low resistivity substrate can dissipate most of the power as heat in the substrate and thus lowers the overall system efficiency. The combined effect of the high dielectric constant and low resistivity of the substrate also has profound effects on the on-chip antenna design as discussed in the next section.

In this paper, we present a fully integrated four-element phased-array receiver with on-chip antennas at 77 GHz implemented in a 130-nm IBM SiGe BiCMOS process. In Section II, we discuss the integration of the on-chip antennas in silicon. Section III shows the system architecture and the details of the

circuit design are presented in Section IV. Finally, we report the experimental results in Section V.

#### II. ANTENNA DESIGN

An antenna converts electrical power in the circuit domain to electromagnetic wave radiations in a propagation medium and *vice versa*. The radiated energy appears as loss if looked at from a pure circuit domain perspective and is thus modeled as a resistance.<sup>2</sup> In addition to this so-called "radiation resistance" which is essential to the antenna operation, a second resistive part is required to model the physical energy loss in the non-ideal metals and the dielectrics. For an antenna excited with a current source, loss and radiated power can be calculated as

$$P_{\text{rad}} = R_{\text{rad}} I^2 / 2$$

$$P_{\text{loss}} = R_{\text{loss}} I^2 / 2$$

(1)

where  $P_{\rm rad}$  is the radiated power,  $P_{\rm loss}$  is the lost power,  $R_{\rm rad}$  is the radiation resistance,  $R_{\rm loss}$  is the loss resistance, and I is the antenna current. Obviously, high loss resistance wastes power and lowers the overall efficiency. In fact, radiation efficiency is directly related to the ratio of loss and radiation resistances. By knowing these two values, radiation efficiency can be calculated as

$$\eta_{\rm rad} = \frac{R_{\rm rad}}{R_{\rm rad} + R_{\rm loss}}.$$

(2)

In this section, we focus on important antenna parameters such as gain and efficiency and compare several antenna configurations suitable for silicon on-chip implementation based on these parameters.

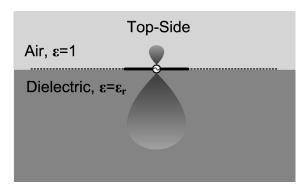

# A. Radiating From Topside Without Ground Shield

The most obvious choice for on-chip antennas is to implement them as metal lines on top of the substrate and radiate upward into the air. In this subsection, we show why this may not be an effective solution by looking at a dipole antenna placed at the boundary of semi-infinite regions of air and dielectric (Fig. 1). Although this over-simplified configuration does not correspond to the practical setting, it guides us to better understand the effects of silicon high dielectric constant on antenna radiation pattern and efficiency. For a dipole antenna seeing the vacuum (or air) on one side and a dielectric on the other side, the ratio of the power coupled into air to the total radiated power is approximated<sup>3</sup> by [9], [10]

$$\frac{P_{\text{air}}}{P_{\text{total}}} = \frac{1}{\varepsilon^{3/2}} \tag{3}$$

where  $P_{\rm air}$  is the radiated power into air,  $P_{\rm total}$  is the total radiated power and  $\epsilon$  is the dielectric constant. From this formula for silicon dielectric ( $\epsilon \sim 11.7$ ) a very small portion of the power radiates into the air (about 3%) and the rest of it couples into silicon. This demonstrates that without any mechanism to reroute the power coupled into silicon substrate, it is not possible to implement a high efficiency antenna on-silicon this way.

<sup>2</sup>Often a reactive part is also used to account for the resulting phase difference between antenna's voltage and current.

Fig. 1. Radiating from top side without ground shield.

Fig. 2. Radiating from top side with on-chip ground shield.

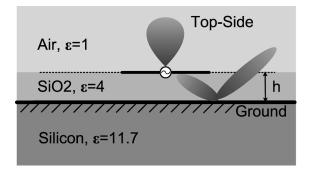

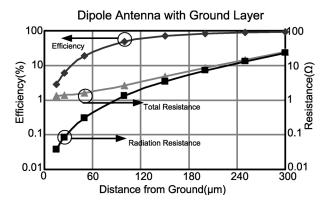

#### B. Radiating From Topside With On-Chip Ground Shield

Another possible option is to incorporate an on-chip ground shield and trying to reflect the radiated energy upward, thus preventing it from coupling into silicon, as shown in Fig. 2. In this case, the on-chip antenna and the ground shield have to be placed inside the SiO<sub>2</sub> due to process limitations. For such a configuration, the distance of the antenna and the ground shield affects the antenna-ground coupling and determines the radiation resistance [18], [19]. Unfortunately, the distance between the bottom of the top metal layer and the top of the lowest metal layer rarely exceeds 15  $\mu$ m in today's process technologies. This small antenna-ground spacing causes a strong coupling between the antenna and the ground layer which lowers the all-important radiation resistance. Fig. 3 shows the results of the electromagnetic simulations of a copper dipole antenna placed over a metal ground plane with a  $SiO_2$  dielectric of thickness, h, sandwiched in between. The dipole dimensions are  $4 \mu m \times 20 \mu m \times 1150 \mu m$ and a moment-based EM simulator, IE3D [26], is used to perform the simulations. The dipole-length is equal to a length of a resonant dipole at 77 GHz which is placed in the boundary of semi-infinite regions of air and SiO2. Based on this simulation, for a spacing of 15  $\mu$ m between the antenna and the ground layer, the radiation resistance is very small (less than 0.1  $\Omega$ ) hence the total resistance is dominated by the ohmic loss of the copper resulting in a radiation efficiency of less than 5%. An option to increase the efficiency of the antenna seems to be the implementation of an off-chip ground shield to increase the distance between the antenna and its ground layer. We will discuss this case in the next subsection.

<sup>&</sup>lt;sup>3</sup>Within a factor of 2.

Fig. 3. Dipole radiation resistance and efficiency.

Fig. 4. Radiating from top side with off-chip ground shield.

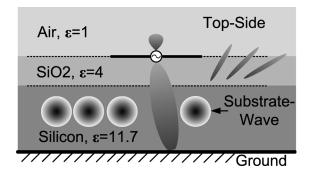

# C. Radiating From Topside With Off-Chip Ground Shield

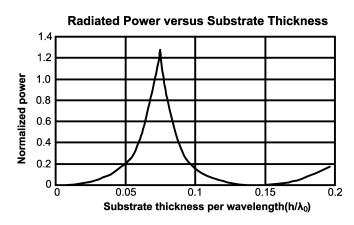

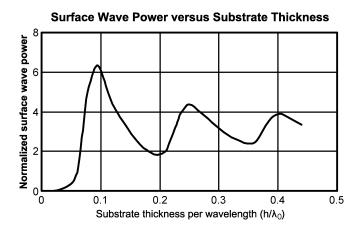

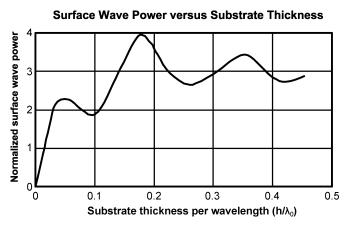

As shown in Fig. 4, an off-chip ground shield can be placed underneath the silicon substrate. In this case, the silicon substrate thickness is much larger than the  ${\rm SiO_2}$  layer and effectively we are dealing with a high dielectric constant substrate ( $\epsilon=11.7$ ). Unfortunately, because of the high dielectric constant of silicon and the large substrate thickness (100  $\mu$ m or more), most of the power gets absorbed into surface-wave power [9]–[11]. If we assume the thickness of  ${\rm SiO_2}$  is negligible compared to that of silicon, then the surface-wave power can be numerically calculated. Based on these results, normalized radiated power and surface-wave power are plotted in Fig. 5 and Fig. 6, respectively. These quantities are normalized to the dipole's free space radiated power given by [9]

$$P_0 = \omega^2 \mu_0^{3/2} \varepsilon_0^{1/2} I^2 d^2 / 12\pi \tag{4}$$

where I is the current,  $\omega$  is the angular frequency, and d is the effective length of the dipole. As is shown in Fig. 5, at 77 GHz the maximum radiated power, which is around  $1.3P_0$ , occurs at the silicon substrate thickness of 290  $\mu$ m (h =  $0.075\lambda_0$ ). However, at this substrate thickness, the power in all the surface wave modes is more than  $3.5P_0$  (Fig. 6), which indicates that even in the case of lossless silicon substrate, the power wasted in the surface wave modes is 2.7 times greater than the useful radiated power. It is important to realize that for a lossy and finite-dimensional substrate, the surface-wave power is either dissipated due to the substrate conductivity or radiated from the edge of the chip and that often results in an undesirable radiation pattern.

Fig. 5. Normalized radiated power for a grounded dipole [9].

Fig. 6. Surface wave power for a grounded dipole [9].

Fig. 7. Radiating from planar back-side.

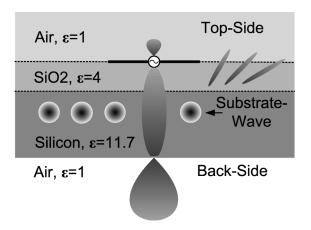

#### D. Radiating From the Planar Backside

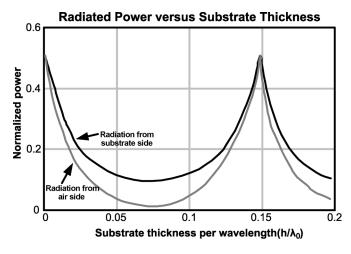

Following the prior discussion, we attempt to determine what happens if we remove any ground shield and radiate from the backside of the chip (see Fig. 7). In this case, based on numerical calculations [9], [11], the normalized radiated and surface-wave powers are plotted in Fig. 8 and Fig. 9, respectively. At 77 GHz, the total radiated power, the sum of the power radiated from the air side and the substrate side, peaks at the silicon substrate thickness of 580  $\mu$ m (h = 0.15 $\lambda$ <sub>0</sub>) and approaches  $P_0$ . At this substrate thickness, the total surface-wave power is

Fig. 8. Normalized radiated power for an ungrounded dipole [9].

Fig. 9. Surface wave power for an ungrounded dipole [9].

around  $3.4P_0$ , which is 3.4 times greater than the power radiated from the air side and the substrate side combined.

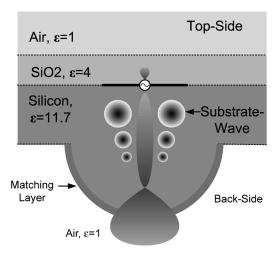

## E. Radiating From the Back-Side Using a Dielectric Lens

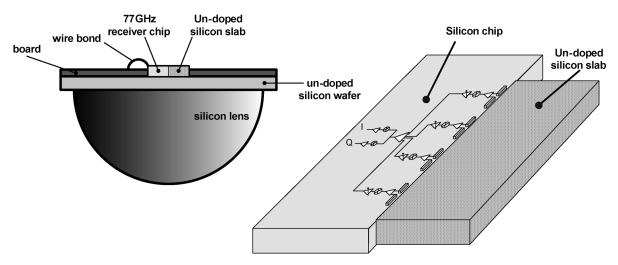

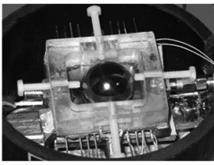

Fortunately, the amount of the total power absorbed into surface-waves depends on the geometry of the substrate. A hemispherical silicon lens with a matching layer can convert the surface-wave power to a useful radiated power [9]-[15]. This configuration is illustrated in Fig. 10. A quarter wave-length matching layer can be used to match the silicon impedance  $(Z_{\rm si}=110~\Omega)$  to air impedance  $(Z_{\rm air}=377~\Omega)$  [16]. In our design, we have used the silicon lens without the matching layer due to the fabrication limitations. In this design, antennas are fabricated by using bottom metal layers to minimize the distance to the substrate. A parallel combination of three bottom metal layers maintains high antenna metal conductivity. To further reduce the substrate loss, the silicon chip is thinned down to 100  $\mu$ m. This minimizes the path length through which the radiated wave travels inside the lossy doped substrate. Due to layout limitations in our design, the antennas are placed at the edge of the chip and a slab of undoped silicon is abutted to the substrate to maintain a uniform dielectric constant substrate underneath the antenna (Fig. 11). For mechanical stability, a 500- $\mu$ m-thick undoped silicon wafer is placed underneath the chip and the silicon lens is mounted on the backside seen in

Fig. 10. Radiating from back side using a silicon lens.

Fig. 11. All of the low-frequency connections are brought to the chip by board metal traces and wire-bond connections. As this setup is highly compatible with flip-chip technology, all of these low-frequency signals can be carried by flip-chip connections as well.

#### III. SYSTEM ARCHITECTURE

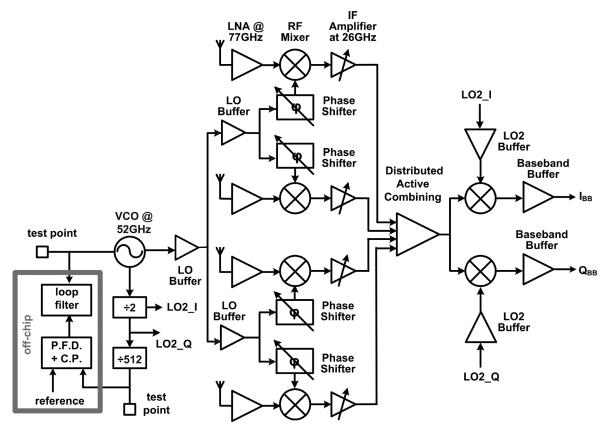

In this section, we describe the block diagram of the 77-GHz four-element phased-array receiver which is part of a complete 77-GHz four-element transceiver. The transmitter and local oscillator (LO) generation circuits are presented in [21] and [23].

Fig. 12 shows the architecture of the receiver chip, which adopts a two-step downconversion scheme with an RF frequency of 76–81 GHz and an IF in the 25–27 GHz. This frequency plan enables us to generate the first and second LO signals with a single frequency synthesizer. It is also noteworthy that the IF is located in the 22–29 GHz radar band, hence a dual-mode radar chip can be potentially developed by bypassing the RF front-end. Each receiver front-end consists of an on-chip dipole antenna, a low-noise amplifier (LNA), an RF mixer, and a dual-mode IF amplifier. The gain of the IF amplifier can be varied by 15 dB using a single digital control bit. The four-path IF signals are combined using a symmetric active combining amplifier, which will be discussed in Section IV. The combined signal is further downconverted to baseband using quadrature paths.

A differential voltage-controlled oscillator (VCO) generates the first LO signals at 52 GHz, which are symmetrically distributed to each RF mixer using differential transmission lines (t-lines). A network of LO buffers is used for LO signal distribution to compensate for the t-line loss and to ensure hard switching of the mixers. The continuous analog phase shifting is performed locally at each RF mixer by an analog phase rotator, which realizes continuous beam steering while accurately compensating for the phase and amplitude deviations. The quadrature second LO is obtained by dividing the first LO frequency by 2 [21], [23]. A frequency divider chain is used to further divide the second LO frequency down to 50 MHz to be locked to an external reference frequency.

At mm-wave frequencies, t-lines are a better choice than inductors for matching purposes. At these frequencies, the required reactance for matching circuits is small. These matching

Fig. 11. Board setup configuration.

Fig. 12. System architecture.

circuits can be implemented by using shielded transmission lines. Other advantages of these shielded transmission lines are accurate modeling, well-defined return path, high isolation, and reduced coupling to the adjacent circuits [8].

#### IV. CIRCUIT DESCRIPTION

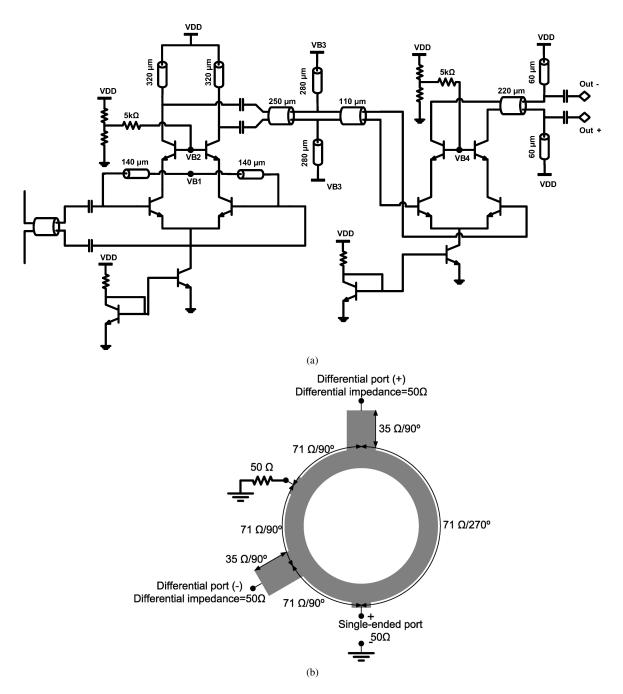

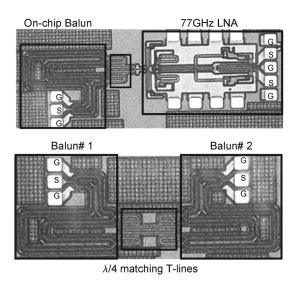

## A. 77-GHz LNA With an On-Chip Balun

The two-stage differential cascode LNA driven by a differential dipole antenna uses shunt and series t-lines for impedance matching [Fig. 13(a)]. The differential input impedance of the LNA and its differential output impedance are designed to be

$50\,\Omega$  and  $100\,\Omega$ , respectively, at 77 GHz. In order to characterize LNA performance independently, a single-ended-to-differential converter, a balun, following a  $\lambda/4$  t-line is placed at the front of the stand-alone LNA test structure, as shown in Fig. 13(b). This combined structure converts the differential  $50\,\Omega$  input impedance of the LNA to single-ended  $50\text{-}\Omega$  impedance which can be easily driven by a single-ended  $50\text{-}\Omega$  waveguide probe.

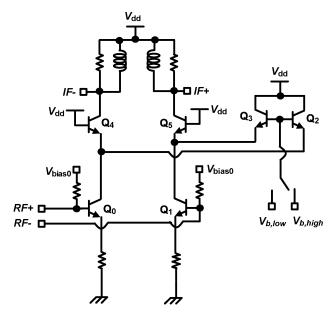

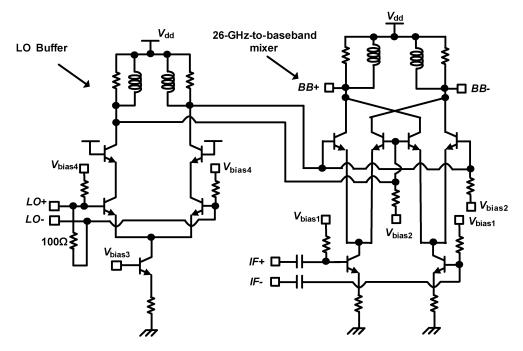

## B. 77-to-26-GHz RF Mixer

A double-balanced current-commuting mixer is employed to downconvert the 77-GHz RF signal to a 25.5-GHz IF, as illustrated in Fig. 14 [27]. AC-coupling capacitors are placed at the

Fig. 13. (a) 77-GHz LNA schematic. (b) Schematic of balun.

RF ports. The RF and LO ports of the mixer are all matched to a differential impedance of  $100 \Omega$ , using t-line stub tuning [22].

The bandwidth of this mixer is primarily determined by the quality factor Q of the resonant load at 26 GHz. The 3-dB bandwidth (BW) of the load impedance is related to Q as

$$BW = \frac{\omega_o}{Q} \tag{5}$$

where  $\omega_o$  is the resonant frequency. The load impedance of a parallel *LC* at resonance is given by [22, p. 307]

$$Z_L \approx \omega_o L Q.$$

(6)

Therefore, the choice of Q is a trade-off between bandwidth and gain. To achieve the desired bandwidth, a Q of 3.5 is the maximum, according to which we choose 0.4-nH inductance and 250- $\Omega$  de-Q resistance to form the load with the capacitance of the transistor parasitic and input impedance of the subsequent stage.

Simulation results indicate the RF mixer achieves 5-dB voltage conversion gain, a 10-GHz bandwidth, and an 11-dB noise figure. They also show an input return loss of 20 dB at the RF port and 11 dB at the LO port. To save chip area, resistive emitter degeneration instead of inductive degeneration is used to enhance the linearity. The common node of the degeneration resistors is connected to the ground instead of a tail current source for better linearity.

Fig. 14. 77-GHz RF mixer.

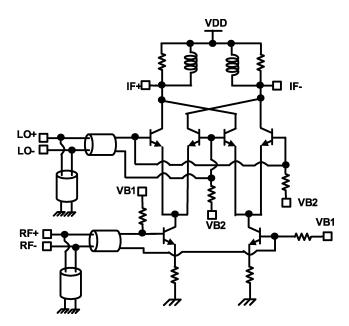

# C. 26-GHz Two-Mode Amplifier

A differential resistively degenerated cascode is used as the 26-GHz amplifier, as shown in Fig. 15. A differential current-bleeding branch consisting of  $Q_2$  and  $Q_3$  is added. The DC bias voltage at the base of  $Q_2$  and  $Q_3$  can be toggled between two values by digital switches, corresponding to a high-gain and a low-gain mode of the amplifier. In high-gain mode,  $Q_2$  and  $Q_3$  are off. In low-gain mode, the gain normalized to its high gain value is approximately given by

$$\frac{A_{v,\text{low}}}{A_{v,\text{high}}} = \left(1 + \frac{A_2}{A_4} \exp\left(\frac{V_{b,\text{low}} - V_{\text{dd}}}{V_T}\right)\right)^{-1} \tag{7}$$

where  $A_2$  and  $A_4$  are the emitter area of  $Q_2$  and  $Q_4$ , respectively, and  $V_{b,\mathrm{low}}$  is the base voltage of  $Q_2$  and  $Q_4$  in the lowgain mode. In this design,  $V_{B,Q_2}$  at low-gain mode is set to  $V_{\mathrm{dd}}$ , and  $A_2/A_4$  is fixed at 11/3. Equation (7) predicts 13.5-dB gain variation between the two modes. The simulation result shows 15-dB gain variation.

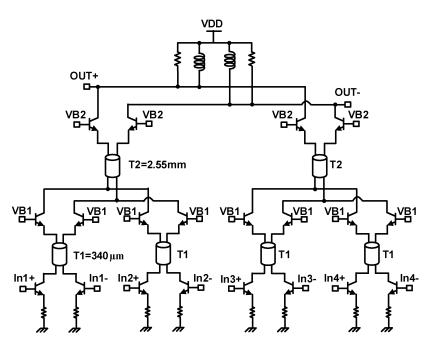

# D. A 26-GHz Signal Combining Amplifier

The four-path 26-GHz signals are combined through a distributed active combining amplifier, as shown in Fig. 16 [27]. Emitter resistive degeneration is implemented at the input transconductors to improve the linearity and accordingly the dynamic range of the system. The current outputs of the transconductors are routed to the combining node via a symmetric two-stage binary structure. A pair of cascode transistors is inserted at each combining junction to isolate the input and output ports, thereby improving the overall stability of the amplifier. The total length of each routing transmission line, T1, is 340  $\mu$ m and that of T2 is roughly 2.55 mm. Both T1 and T2 use a differential t-line structure with ground and side metal shields to minimize the substrate loss and cross coupling. Matched transmission line terminations are obtained by choosing the appropriate bias current so that the conductance  $q_m$  of the cascade transistors is matched to the real t-line conductance.

Fig. 15. 26-GHz two-gain mode amplifier.

For the operating frequency of  $\omega_0$ , the imaginary part of the emitter-base admittance,  $j\omega_0c_\pi$ , is much smaller than  $g_m$  if the transistor transition frequency  $\omega_T$  is much higher than  $\omega_0$ . Therefore, a matched termination can be achieved even without additional passive tuning. In this work, we dedicated 1-mA DC bias current to each branch.  $T_1$  is designed to exhibit 64- $\Omega$  odd-mode impedance, while  $T_2$  has an odd impedance of 32  $\Omega$ . Simulations show that the return loss is better than 10 dB at the terminations of the transmission lines at both levels. The differential output of the amplifier is loaded with an LC tank with parallel resistors to improve the bandwidth.

## E. 26-GHz Quadrature Mixer

A pair of double-balanced mixers driven by quadrature LO signals are used to perform frequency translation from 26 GHz to baseband, one of which is shown in Fig. 17. The 26-GHz signals are coupled into the mixer transconductance stage through 0.9-pF MIM capacitors. The input differential pair is degenerated with  $30-\Omega$  resistors at the emitter to improve linearity.

The LO port of the mixer is fed by a 26-GHz buffer which is used to compensate the LO signal loss through the distribution network, ensuring the differential LO amplitude applied to the mixer is larger than 200 mV so that the mixer gain is saturated. The input matching of the LO buffer is provided by a 100- $\Omega$  resistor directly connected between the differential inputs. Although matching network composed of inductors and capacitors can provide additional voltage gain, this solution is prohibited by the limited silicon area. The LO buffer is loaded with 0.6-nH spiral inductors and  $320~\Omega$  de-Q resistors, providing a gain of 15 dB. With 280- $\Omega$  load resistor, the second mixer achieves 6-dB conversion gain and 8-GHz IF-referred bandwidth. The mixer core consumes 4-mA DC current and the LO buffer drains 1 mA.

# V. EXPERIMENTAL RESULTS

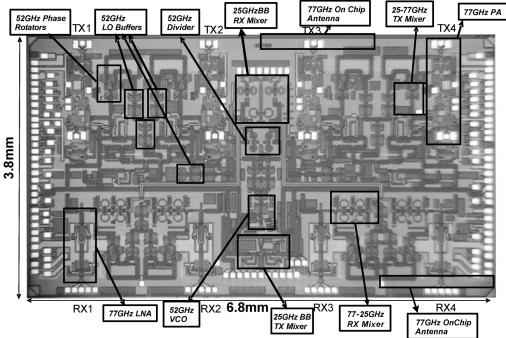

The 77-GHz phased array is fabricated in a 0.13- $\mu$ m SiGe BiCMOS process with a  $f_T$  of 200 GHz for SiGe HBT devices.

Fig. 16. 26-GHz combining amplifier.

Fig. 17. 26-GHz-to-baseband mixer and 26-GHz LO buffer.

The receiver section occupies roughly 9 mm $^2$  of the 6.8 mm  $\times$  3.8 mm total chip. Fig. 18 shows the die micrograph.

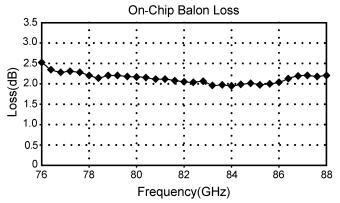

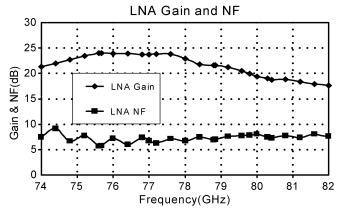

To accurately characterize the receiver performance, a stand-alone LNA with integrated balun is measured. One of the important parameters necessary for accurate de-embedding of the stand-alone LNA measurements is the loss of the balun and the following  $\lambda/4$  t-line. Two identical baluns including the matching transmission lines are designed and connected together at their differential nodes, as shown in Fig. 19. The loss of the two series identical structures is expected to be twice that of a single one. The measured balun loss and the LNA performance versus frequency are shown in Fig. 20 and

Fig. 21, respectively. Stand-alone LNA peak gain of 23.8 dB is measured at 77 GHz with a 3-dB bandwidth of more than 6 GHz, while the lowest noise figure of 5.7 dB is measured at 75.7 GHz. The LNA consumes 17.5 mA from a 3.5-V supply.

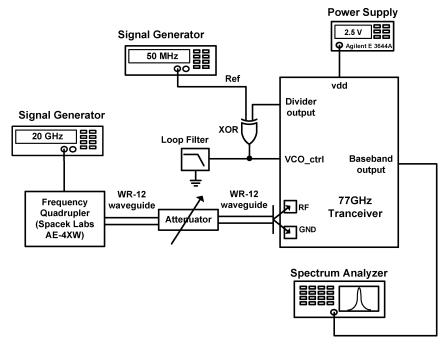

Fig. 22 illustrates the test setup for measuring the receiver gain. The input signal at 77-GHz range is provided by a frequency quadrupler capable of delivering output frequency from 60–90 GHz. The input of the frequency quadrupler is supplied by signal generator working up to 26.5 GHz. The power of the input signal can be adjusted by a variable linear attenuator. A WR-12 planar wafer probe is used to feed the single-ended signal to LNA input. The external connections between W-band

Fig. 18. Chip micrograph.

Fig. 19. 77-GHz LNA with on-chip balun.

components are built using WR-12 waveguides. The microwave input power is calibrated up to the probe tip using an Agilent E4418B power meter with W-band power sensor. An exclusive OR (XOR) logic gate acting as a phase detector and a first-order *RC* low-pass filter complete the PLL which locks the phase and frequency of the 52-GHz VCO to a 50-MHz reference provided by a signal generator. The baseband outputs are characterized using Agilent 4448A spectrum analyzer. The same setup is also used for receiver noise figure measurement, except the RF inputs are replaced with a W-band noise source.

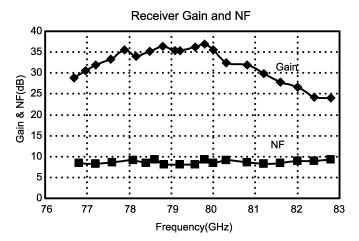

The electrical performance of the receiver is characterized after laser trimming the antennas. A 37-dB single-path receiver gain (Fig. 23) is measured at 79.8 GHz with a 2-GHz bandwidth,

Fig. 20. Measured on-chip balun loss.

Fig. 21. LNA gain and noise figure.

corresponding to an inferred array gain of 49 dB. The minimum receiver noise figure is measured to be 8 dB (at 78.8 GHz).

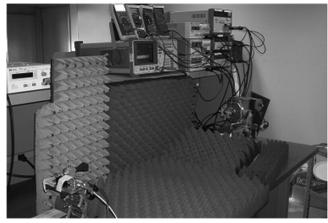

The radiation performance of the complete receiver is measured using the setup shown in Fig. 11 where a printed circuit

Fig. 22. Receiver test setup.

Fig. 23. Single path receiver gain and noise figure.

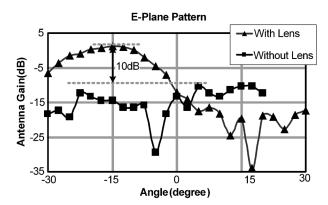

board (PCB) provides the supply as well as low-frequency and digital control signals to the chip and takes the baseband signal out using wirebond connections. A W-band standard horn antenna irradiates the receiver (Fig. 24). The peak measured antenna gain is +2 dBi. Based on the simulations, this gain can be further improved by 4 to 5 dB using a smaller lens with a quarter-wavelength matching layer. Fig. 25 shows the measured deembedded E-plane single-element dipole radiation pattern with and without the lens. Based on this measurement, the lens improves the gain by more than 10 dB.

The measurement results are summarized in Table I.

# VI. CONCLUSION

The reported phased-array receiver, combined with the phased-array transmitter in [21] and [23], forms the first fully integrated silicon based phased-array transceiver with on-chip

TABLE I MEASUREMENT SUMMARY

| Receiver Conversion Gain                                  | +37dB (per element) |

|-----------------------------------------------------------|---------------------|

| Inferred Array Gain                                       | +49dB               |

| Receiver 3dB-bandwidth                                    | 2GHz                |

| Receiver Minimum NF                                       | 8dB (per element)   |

| LNA Gain                                                  | +23dB               |

| LNA 3dB-bandwidth                                         | 6GHz                |

| LNA Minimum NF                                            | 5.7dB               |

| LNA output referred 1dB                                   | -5.5dBm             |

| Antenna Gain                                              | +2dBi               |

| Current consumption:                                      |                     |

| Each LNA (@3.5V)                                          | 17.5mA              |

| Each down-conversion path (@2.5V)                         | 40mA                |

| Entire 4-path receiver with frequency synthesizer (@2.5V) | 420mA               |

|                                                           |                     |

antennas at 77 GHz. In the receiver, a two-step down-conversion scheme is used with a single VCO. The signal combining is performed using a novel distributed active combining amplifier at IF. In the LO path, a cross-coupled quadrature injection locked frequency divider (QILFD) divides the 52-GHz VCO frequency by a factor of 2 and is followed by a divide-by-512 divider chain. Conversion gain of more than 37 dB, 2 GHz BW, and 8 dB noise figure are achieved. The antenna gain of +2 dBi is achieved in the silicon substrate. We have shown that the lens improves the gain by more than 10 dB.

## ACKNOWLEDGMENT

The authors thank DARPA's trusted foundry program and IBM for the chip fabrication. They also appreciate valuable help from D. Rutledge, S. Weinreb, G. Rebeiz, T. Yu, Y. Wang,

Fig. 24. Antenna measurement setup.

Fig. 25. E-plane antenna gain.

E. Keehr, A. Hassibi, and P. Focardi. The technical support for CAD tools from Agilent Technologies, Zeland Software Inc., Ansoft Corp., and Integrated Engineering Software is also appreciated.

## REFERENCES

- [1] A. J. Joseph, D. L. Harame, B. Jagannathan, D. Coolbaugh, D. Ahlgren, J. Magerlein, L. Lanzerotti, N. Feilchenfeld, S. St Onge, J. Dunn, and E. Nowak, "Status and direction of communication technologies—SiGe BiCMOS and RFCMOS," *Proc. IEEE*, vol. 93, no. 9, pp. 1539–1558, Sep. 2005.

- [2] X. Guan, H. Hashemi, and A. Hajimiri, "A fully integrated 24-GHz eight-element phased-array receiver in silicon," *IEEE J. Solid-State Circuits*, vol. 39, no. 12, pp. 2311–2320, Dec. 2004.

- [3] B. A. Floyd, S. K. Reynolds, U. R. Pfeiffer, T. Zwick, T. Beukema, and B. Gaucher, "SiGe bipolar transceiver circuits operating at 60 GHz," *IEEE J. Solid-State Circuits*, vol. 40, no. 1, pp. 156–167, Jan. 2005.

- [4] B. Razavi, "A 60-GHz CMOS receiver front-end," *IEEE J. Solid-State Circuits*, vol. 41, no. 1, pp. 17–22, Jan. 2005.

- [5] C. H. Doan, S. Emami, A. M. Niknejad, and R. W. Brodersen, "Millimeter-wave CMOS design," *IEEE J. Solid-State Circuits*, vol. 40, no. 1, pp. 144–155, Jan. 2005.

- [6] Federal Communications Commission, FCC part 15, sec. 15.253.

- [7] ECC Decision of 19 March 2004 on the Frequency Band 77–81 GHz to be Designated for the Use of Automotive Short Range Radars (ECC/DEC/(04)03), Eur. Radiocommun. Office. Copenhagen, Denmark, 2004 [Online]. Available: http://www.ero.dk

- [8] A. Komijani and A. Hajimiri, "A wideband 77 GHz, 17.5 dBm power amplifier in silicon," in *Proc. CICC*, Sep. 2005, pp. 571–575.

- [9] D. B. Rutledge et al., "Integrated-circuit antennas," in Infrared and Millimeter-Waves. New York: Academic, 1983, pp. 1–90.

- [10] N. Engheta and C. H. Papas, Radio Sci., vol. 17, pp. 1557–1566, 1982.

- [11] H. Kogelnik, "Theory of dielectric waveguides," in *Integrated Optics*, T. Tamir, Ed. New York: Springer-Verlag, ch. 2.

- [12] N. G. Alexopoulos, P. B. Katehi, and D. B. Rutledge, "Substrate optimization for integrated circuit antennas," *IEEE Trans. Microw. Theory Tech.*, vol. 83, no. 7, pp. 550–557, Jul. 1983.

- [13] B. Chantraine-Barès, R. Sauleau, L. Le Coq, and K. Mahdjoubi, "A new accurate design method for millimeter-wave homogeneous dielectric substrate lens antennas of arbitrary shape," *IEEE Trans. Antennas Propagat.*, vol. 53, no. 3, pp. 1069–1082, Mar. 2005.

- [14] D. F. Filipovic, G. P. Gauthier, S. Raman, and G. M. Rebeiz, "Off axis properties of silicon and quartz dielectric lens antennas," *IEEE Trans. Antennas Propagat.*, vol. 45, no. 5, pp. 760–766, May 1997.

- [15] T. Nagatsuma et al., "Millimeter-wave photonic integrated circuit technologies for high-speed wireless communications applications," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2004, pp. 448–449.

- [16] M. J. M. van der Vorst, P. J. I. de Maagt, and M. H. A. J. Herben, "Effect of internal reflections on the radiation properties and input admittance of integrated lens antennas," *IEEE Trans. Microw. Theory Tech.*, vol. 47, no. 9, pp. 1696–1704, Sep. 1999.

- [17] P. Focardi, W. R. McGrath, and A. Neto, "Design guidelines for terahertz mixers and detectors," in *Infrared and Millimeter Waves and 13th Int. Conf. Terahertz Electronics*, Sep. 19–23, 2005, vol. 2, pp. 624–625.

- [18] T. Al-Attar, A. Hassibi, and T. H. Lee, "A 77 GHz monolithic IMPATT transmitter in standard CMOS technology," in *Proc. IEEE MTT-S Int. Microwave Symp.*, Jun. 12–17, 2005, pp. 1571–1574.

- [19] T. Al-Attar and T. H. Lee, "Monolithic integrated millimeter-wave IM-PATT transmitter in standard CMOS technology," *IEEE Trans. Microw. Theory Tech.*, vol. 53, no. 11, pp. 3557–3561, Nov. 2005.

- [20] A. Babakhani, X. Guan, A. Komijani, A. Natarajan, and A. Hajimiri, "A 77 GHz four-element phased-array receiver with on-chip dipole antennas in silicon," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2006, pp. 180–181.

- [21] A. Natarajan, A. Komijani, X. Guan, A. Babakhani, Y. Wang, and A. Hajimiri, "A 77 GHz phased array transmitter with local lo-path phase-shifting in silicon," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2006, vol. 49, pp. 182–183.

- [22] D. M. Pozar, Microwave Engineering. New York: Wiley, 1998.

- [23] A. Natarajan, A. Komijani, X. Guan, A. Babakhani, and A. Hajimiri, "A 77 GHz phased array transmitter with local LO-path phase-shifting in silicon," *IEEE J. Solid-State Circuits*, vol. 41, no. 12, pp. 2807–2819, Dec. 2006.

- [24] B. Jagannathan *et al.*, "Self-aligned SiGe NPN transistors with 285 GHz  $f_{max}$  and 207 GHz  $f_T$  in a manufacturable technology," *IEEE Electron Device Lett.*, vol. 23, no. 5, pp. 258–260, May 2002.

- [25] High Frequency Structure Simulator (HFSS). [Online]. Available: http://www.ansoft.com

- [26] MoM-Based Electromagnetic Simulator (IE3D). [Online]. Available: http://www.zeland.com

- [27] X. Guan, "Microwave integrated phased array receivers in silicon," Ph.D. dissertation, Caltech, Pasadena, Sep. 2005.

**Aydin Babakhani** (S'03) received the B.S. degree in electronics engineering from Sharif University of Technology, Tehran, Iran, in 2003, and the M.S. degree in electrical engineering from the California Institute of Technology (Caltech), Pasadena, in 2005. He is currently working toward the Ph.D. degree at Caltech

Mr. Babakhani is the Vice Chair of the IEEE Microwave Theory and Techniques Society Metro LA/SFV Joint Sections MTT-S Chapter 17.1. He was the recipient of the Grand Prize in the Stan-

ford-Berkeley-Caltech Innovators Challenge in 2006, ISSCC 2005 Analog Devices Inc. Outstanding Student Designer Award, and Caltech Special Institute Fellowship and Atwood Fellowship in 2003. He was also the Gold medal winner of the National Physics Competition in 1998 and the Gold Medal winner of the 30th International Physics Olympiad, Padova, Italy, in 1999.

**Arun Natarajan** (S'03) received the B.Tech. degree in electrical engineering from the Indian Institute of Technology, Madras, in 2001, and the M.S. degree from the California Institute of Technology (Caltech), Pasadena, in 2003. He is currently working toward the Ph.D. degree at Caltech.

During the summer of 2005, he was a Design Engineer at the IBM T. J. Watson Research Center, Yorktown Heights, NY, where he worked on integrated circuits for high-frequency wireless receivers. His current research interests include design of

integrated high-frequency circuits, wireless transceivers, and modeling of parasitic coupling in ICs.

Mr. Natarajan received the Caltech Atwood Fellowship in 2001, the Analog Devices Outstanding Student IC Designer Award in 2004, and the IBM Research Fellowship in 2005.

Xiang Guan (S'99–M'05) received the B.S. degree in electrical engineering from Tsinghua University, Beijing, China, in 1996, the M.Eng. degree in electrical engineering from the National University of Singapore, Singapore, in 2000, and the Ph.D. degree in electrical engineering from the California Institute of Technology, Pasadena, in 2005.

From 1996 to 1997, he was a visiting researcher at the Integrated Circuits Group, Instituto Superior Tecnico in Lisbon, Portugal, where he was involved in developing a data acquisition chip for electrocardio-

gram telemonitoring devices. During the summer of 2003, he interned at the IBM Thomas J. Watson Research Center, Yorktown Heights, NY, where he designed CMOS RF ICs for WCDMA applications. In 2005, he joined Agilent Laboratories, Palo Alto, CA, as a Member of Research Staff developing integrated ultra-wideband RF front-ends for next-generation semiconductor test equipments. In 2006, he joined SiBeam, Inc., Sunnyvale, CA, as a Senior Microwave and RF Engineer.

Dr. Guan was a co-recipient of the 2004 JSSC Best Paper Awards. He was a co-recipient of the Grand Prize in the Stanford Innovators Challenge in 2006. He also received the Schlumberger Fellowship in 2000 and the Analog Devices Outstanding Student Designer Award in 2002.

**Abbas Komijani** (S'98) received the B.S. and M.S. degrees in electronics engineering from the Sharif University of Technology, Tehran, Iran, in 1995 and 1997, respectively. He is currently working toward the Ph.D. degree at the California Institute of Technology (Caltech), Pasadena, CA.

From 1997 to 1999, he was a Senior Design Engineer with Emad Semiconductors, Tehran, where he worked on CMOS chipsets for voiceband applications. From 1999 to 2000, he was a Senior Design Engineer with Valence Semiconductors, Irvine, CA,

where he was involved with data converters for voice over Internet Protocol (VoIP) applications. His research interests include high-frequency power amplifiers, wireless transceivers, phased-array architectures, and delta-sigma data converters.

Mr. Komijani was the recipient of the Silver Medal in the National Mathematics Olympiad in 1991, Caltech's Atwood Fellowship in 2000, the CICC Best Student Paper Award in 2004, the Analog Devices Outstanding Student Designer Award in 2005, the Grand Prize in the Stanford-Berkeley-Caltech Innovators' Challenge in 2006, and the Outstanding Ph.D. Student Award from the Association of Professors and Scholars of Iranian Heritage (APSIH) in 2006.

Ali Hajimiri (S'95–M'99) received the B.S. degree in electronics engineering from the Sharif University of Technology, Tehren, Iran, and the M.S. and Ph.D. degrees in electrical engineering from Stanford University, Stanford, CA, in 1996 and 1998, respectively.

He was a Design Engineer with Philips Semiconductors, where he worked on a BiCMOS chipset for GSM and cellular units from 1993 to 1994. In 1995, he was with Sun Microsystems, where he worked on the UltraSPARC microprocessor's cache RAM design methodology. During the summer of 1997, he

was with Lucent Technologies (Bell Labs), Murray Hill, NJ, where he investigated low-phase-noise integrated oscillators. In 1998, he joined the Faculty of the California Institute of Technology, Pasadena, where he is an Associate Professor of Electrical Engineering and the Director of Microelectronics Laboratory. He is also a cofounder of Axiom Microdevices Inc. His research interests are high-speed and RF integrated circuits.

Dr. Hajimiri is the author of The Design of Low Noise Oscillators (Kluwer, 1999) and holds several U.S. and European patents. He is an Associate Editor of the IEEE JOURNAL OF SOLID-STATE CIRCUITS and a member of the Technical Program Committee of the IEEE International Solid-State Circuits Conference (ISSCC). He has also served as an Associate Editor of IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS: PART II, a member of the Technical Program Committees of the International Conference on Computer Aided Design (ICCAD), a Guest Editor of the IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES, and on the Guest Editorial Board of Transactions of Institute of Electronics, Information and Communication Engineers of Japan (IEICE). He was selected to the top 100 innovators (TR100) list in 2004 and is a Fellow of Okawa Foundation. He is the recipient of Caltech's Graduate Students Council Teaching and Mentoring award as well as Associated Students of Caltech Undergraduate Excellence in Teaching Award. He was the Gold Medal winner of the National Physics Competition and the Bronze Medal winner of the 21st International Physics Olympiad, Groningen, The Netherlands. He was a co-recipient of the IEEE JOURNAL OF SOLID-STATE CIRCUITS Best Paper Award of 2004, the ISSCC Jack Kilby Outstanding Paper Award, two times co-recipient of CICC's best paper awards, and a three times winner of the IBM faculty partnership award as well as the National Science Foundation CAREER